This article needs additional citations for verification. (February 2024) |

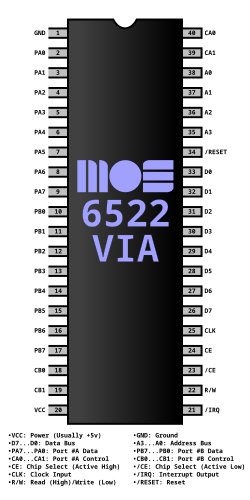

The MOS Technology 6522 Versatile Interface Adapter (VIA) is an integrated circuit that was designed and manufactured by MOS Technology as an I/O port controller for the 6502 family of microprocessors. It provides two bidirectional 8-bit parallel I/O ports, two 16-bit timers (one of which can also operate as an event counter), and an 8-bit shift register for serial communications or data conversion between serial and parallel forms. The direction of each bit of the two I/O ports can be individually programmed. In addition to being manufactured by MOS Technology, the 6522 was second sourced by other companies including Rockwell and Synertek.

The 6522 was widely used in computers of the 1980s, particularly Commodore's machines,[1] and was also a central part of the designs of the Apple III, Oric-1 and Oric Atmos, BBC Micro, Victor 9000/Sirius 1 and Apple Macintosh. Video game platforms such as the Vectrex also used the 6522, as did the 1984 through 1989 Corvette digital dash cluster. A high speed, CMOS version, the W65C22, is produced by the Western Design Center (WDC).

Input/output ports

editThe VIA contains 20 I/O lines, which are organised into two 8-bit bidirectional ports (or 16 general-purpose I/O lines) and four control lines (for handshaking and interrupt generation). The directions for all 16 general lines (PA0-7, PB0-7) can be programmed independently. The control lines can be programmed to generate an interrupt when activated (all four), latch the corresponding I/O port (CA1 and CB1), automatically generate handshaking signals for devices on the I/O ports, or operate as plain program-controlled outputs (CA2 and CB2). CB1 and CB2 are also used as the clock input and the data line for the shift register, precluding their use for other functions while the shift register is enabled.

Timers

editThe VIA provides two 16-bit timer/counters. Each can be used in one-shot (monostable) "interval timer" mode; timer 1 can also be used in "free-running" (divider/square wave) mode, in which the timer is automatically reloaded with the initial count when it reaches zero, and timer 2 can also be used in "pulse counting" mode, in which the timer will count the high-to-low state transitions of pin PB6 (the 7th bit of parallel I/O port B). In the one-shot mode, each timer continues free-running so that the time since zero was reached can be determined, but no further interrupt is issued until the timer is restarted. Each timer can generate an interrupt when it reaches zero, and timer 1 can also output pulses (in the interval timer mode) or square waves (in the free-running mode) on pin PB7 (the 8th bit of port B). Timer 2 can be used to provide the clock frequency for the shift register. A useful feature of the free-running mode is that the 16-bit counter latch can be loaded with a new count without reloading the counter, so that it will load the new count only after the current count reaches zero, seamlessly changing the output frequency. This feature of timer 1, combined with its ability to output to pin PB7, can be used to generate complex waveforms, for example pulse-width modulation signals, frequency sweeps, or bi-phase or FM-encoded serial bit streams.[2]

Shift register

editThe VIA's shift register is bidirectional, 8 bits wide, and can run from either a timer-generated clock (from timer 2), the CPU clock, or an external source on line CB1. The serial input/output is on line CB2, and CB1 can also be programmed to output a bit clock for external clocked serial devices.

IRQ output

editThe NMOS 6522 has an open drain IRQ output that may be used in wired-OR interrupt circuits. The WDC W65C22S, in contrast, has a totem pole IRQ output that must be isolated from a wired-OR circuit by a Schottky diode, due to the fact that the totem pole output actively drives the IRQ pin high when the W65C22S is not interrupting. This specific issue is resolved on the WDC W65C22N which is fitted with an open-drain IRQ output.[3]

Bugs

editDue to a design defect, if the edge on CB1 falls within a few nanoseconds of the falling edge of the ϕ2 (phase–2) clock, the CB1 edge will be ignored, causing the loss of a bit and framing errors on subsequent data.

A workaround is put the external clock signal into the D input of a 74ACT74 flip-flop, run the flop's Q output to the 6522's CB1 pin, and clock the flip-flop with ϕ0 or ϕ2.[4]

The serial shift register bug was corrected in the California Micro Devices CMD G65SC22[citation needed] and in the MOS 6526, the latter device which Commodore used in place of the 6522 from the Commodore 64 onwards.

Aside from the aforementioned shift register bug, there was a potential register corruption problem that usually only occurred in systems using the 6522 with a microprocessor having a non-6502 bus architecture, such as a Motorola 68000. If the address lines changed while chip select was low (inactive) but the ϕ2 clock input was high (active), register contents could be changed despite the fact that the chip was not selected. This was fixed in some but not all of the CMOS versions.

References

edit- ^ The [Commodore] 1541 floppy disc drive has two chips of the type MOS 6522... [dead link]

- ^ 1982 MOS Technology Data Catalog, pgs. 2-54 and 2-55

- ^ W65C22 Versatile Interface Adapter (VIA)

- ^ Wilson, Garth