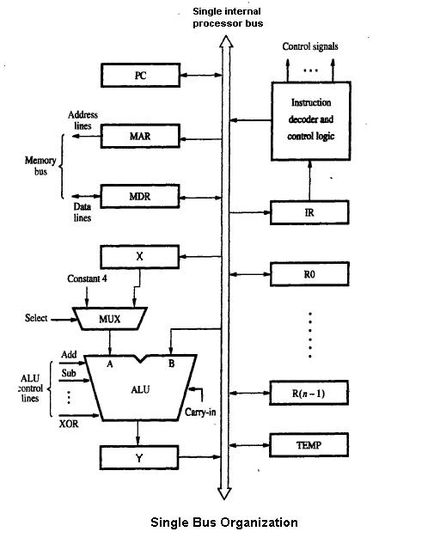

A data path is a collection of functional units such as arithmetic logic units (ALUs) or multipliers that perform data processing operations, registers, and buses.[1] Along with the control unit it composes the central processing unit (CPU).[1] A larger data path can be made by joining more than one data paths using multiplexers.

A data path is the ALU, the set of registers, and the CPU's internal bus(es) that allow data to flow between them.[2]

The simplest design for a CPU uses one common internal bus. Efficient addition requires a slightly more complicated three-internal-bus structure.[3] Many relatively simple CPUs have a 2-read, 1-write register file connected to the 2 inputs and 1 output of the ALU.

During the late 1990s, there was growing research in the area of reconfigurable data paths—data paths that may be re-purposed at run-time using programmable fabric—as such designs may allow for more efficient processing as well as substantial power savings.[4]

Finite state machine with data path

editA finite-state machine with data path (FSMD) is a mathematical abstraction which combines a finite-state machine, which controls the program flow, with a data path. It can be used to design digital logic or computer programs.[5][6]

FSMDs are essentially sequential programs in which statements have been scheduled into states, thus resulting in more complex state diagrams. Here, a program is converted into a complex state diagram in which states and arcs may include arithmetic expressions, and those expressions may use external inputs and outputs as well as variables. The FSMD level of abstraction is often referred to as the register-transfer level.

FSMs do not use variables or arithmetic operations/conditions, thus FSMDs are more powerful than FSMs. An FSMD is equivalent to a Turing machine in expressiveness.

References

edit- ^ a b Null, Linda; Lobur, Julia (2006). The Essentials of Computer Organization and Architecture. Jones & Bartlett Learning. p. 2016. ISBN 978-0-7637-3769-6.

All computers have a CPU that can be divided into two pieces. The first is the datapath, which is a network of storage units (registers) and arithmetic and logic units... connected by buses... where the timing is controlled by clocks.

- ^ Edward Bosworth. "Overview of Computer Architecture".

- ^ Edward Bosworth. "CPU Bus Structure".

- ^ J. R. Hauser and J. Wawrzynek, Garp: a MIPS processor with a reconfigurable coprocessor, FCCM’97, 1997, pp. 12–21. Archived 2017-09-22 at the Wayback Machine

- ^ Zhu, Jianwen; Gajski, Daniel D. (1999-03-01). "A unified formal model of ISA and FSMD". Proceedings of the seventh international workshop on Hardware/Software codesign - CODES '99. New York, NY, USA: Association for Computing Machinery. pp. 121–125. doi:10.1145/301177.301504. ISBN 978-1-58113-132-1. S2CID 5426988.

- ^ Hsu, Y.C.; Liu, T.Y.; Tsai, F.S.; Lin, S.Z.; Yu, C. (1994-12-05). "Digital design from concept to prototype in hours". Proceedings of APCCAS'94 - 1994 Asia Pacific Conference on Circuits and Systems. pp. 175–181. doi:10.1109/APCCAS.1994.514545. ISBN 0-7803-2440-4. S2CID 61056791.