Electronic circuit simulation uses mathematical models to replicate the behavior of an actual electronic device or circuit. Simulation software allows for the modeling of circuit operation and is an invaluable analysis tool. Due to its highly accurate modeling capability, many colleges and universities use this type of software for the teaching of electronics technician and electronics engineering programs. Electronics simulation software engages its users by integrating them into the learning experience. These kinds of interactions actively engage learners to analyze, synthesize, organize, and evaluate content and result in learners constructing their own knowledge.[1]

Simulating a circuit’s behavior before actually building it can greatly improve design efficiency by making faulty designs known as such, and providing insight into the behavior of electronic circuit designs. In particular, for integrated circuits, the tooling (photomasks) is expensive, breadboards are impractical, and probing the behavior of internal signals is extremely difficult. Therefore, almost all IC design relies heavily on simulation. The most well known analog simulator is SPICE. Probably the best known digital simulators are those based on Verilog and VHDL.

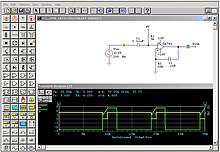

Some electronics simulators integrate a schematic editor, a simulation engine, and an on-screen waveform display (see Figure 1), allowing designers to rapidly modify a simulated circuit and see what effect the changes have on the output. They also typically contain extensive model and device libraries. These models typically include IC specific transistor models such as BSIM, generic components such as resistors, capacitors, inductors and transformers, user defined models (such as controlled current and voltage sources, or models in Verilog-A or VHDL-AMS). Printed circuit board (PCB) design requires specific models as well, such as transmission lines for the traces and IBIS models for driving and receiving electronics.

Types

editWhile there are strictly analog[2] electronics circuit simulators, popular simulators often include both analog and event-driven digital simulation[3] capabilities, and are known as mixed-mode or mixed-signal simulators if they can simulate both simultaneously.[4] An entire mixed signal analysis can be driven from one integrated schematic. All the digital models in mixed-mode simulators provide accurate specification of propagation time and rise/fall time delays.

The event-driven algorithm provided by mixed-mode simulators is general-purpose and supports non-digital types of data. For example, elements can use real or integer values to simulate DSP functions or sampled data filters. Because the event-driven algorithm is faster than the standard SPICE matrix solution, simulation time is greatly reduced for circuits that use event-driven models in place of analog models.[5]

Mixed-mode simulation is handled on three levels: with primitive digital elements that use timing models and the built-in 12 or 16 state digital logic simulator, with subcircuit models that use the actual transistor topology of the integrated circuit, and finally, with inline Boolean logic expressions.

Exact representations are used mainly in the analysis of transmission line and signal integrity problems where a close inspection of an IC’s I/O characteristics is needed. Boolean logic expressions are delay-less functions that are used to provide efficient logic signal processing in an analog environment. These two modeling techniques use SPICE to solve a problem while the third method, digital primitives, uses mixed mode capability. Each of these methods has its merits and target applications. In fact, many simulations (particularly those which use A/D technology) call for the combination of all three approaches. No one approach alone is sufficient.

Another type of simulation used mainly for power electronics represent piecewise linear[6] algorithms. These algorithms use an analog (linear) simulation until a power electronic switch changes its state. At this time a new analog model is calculated to be used for the next simulation period. This methodology both enhances simulation speed and stability significantly.[7]

Complexities

editProcess variations occur when the design is fabricated and circuit simulators often do not take these variations into account. These variations can be small, but taken together, they can change the output of a chip significantly.

Temperature variation can also be modeled to simulate the circuit's performance through temperature ranges.[8]

Simulation from admittance matrix

editA common method of simulating linear circuits systems is with admittance matrices, or Y matrices. The technique involves modeling the individual linear components as an N port admittance matrix, inserting the component Y matrix into a circuits nodal admittance matrix, installing port terminations at nodes that contain ports, eliminating ports without nodes though Kron reduction, converting the final Y matrix to an S or Z matrix as needed, and extracting desired measurements from the Y, Z, and/or S matrix.

Simple Chebyshev filter example

editA fifth order, 50 ohm, Chebyshev filter with 1dB of pass band ripple and cutoff frequency of 1GHz designed using the Chebyshev Cauar topology and subsequent impedance and frequency scaling produces the elements shown in the table and Micro-cap schematic below.

| element | g-value | Type | scaled for

50 ohms and 1GHz |

nodes |

|---|---|---|---|---|

| P1 | 1 | port | 50 | 1 |

| L1 | 2.1348815 | inductor | 1.6988847E-08 | 1, 2 |

| C1 | 1.0911073 | capacitor | 3.4731024E-12 | 2, 0 |

| L2 | 3.0009229 | inductor | 2.3880586E-08 | 2, 3 |

| C2 | 1.0911073 | capacitor | 3.4731024E-12 | 3, 0 |

| L3 | 2.1348815 | inductor | 1.6988847E-08 | 3, 4 |

| P2 | 1 | port | 50 | 4 |

Modeling the 2 port Y parameters

editThe table above provides a list of ideal elements to model along with a node attachments to simulate. Next, each non-port element must be converted into a 2X2 Y parameter model for each frequency to be simulated. For this example, a frequency of 1GHz is selected.

Elements connected to node 0, the ground node, do not need their respective Y12 or Y21 calculated, and are shown as "n/a" in the table.

| element | admittance at 1GHz | Y11, Y22 at 1GHz | Y12, Y21 at 1GHz | nodes |

|---|---|---|---|---|

| P1 | n/a | n/a | n/a | 1 |

| L1 | -J0.0093682013 | -J0.0093682013 | J0.0093682013 | 1, 2 |

| C1 | j0.021822146 | j0.021822146 | n/a | 2, 0 |

| L2 | -J0.0066646164 | -J0.0066646164 | J0.0066646164 | 2, 3 |

| C2 | j0.021822146 | j0.021822146 | n/a | 3, 0 |

| L3 | -J0.0093682013 | -J0.0093682013 | J0.0093682013 | 3, 4 |

| P2 | n/a | n/a | n/a | 4 |

Inserting the 2 port Y parameters into the nodal admittance matrix

editIt should be remembered that while Ideal inductor and capacitor modals consist of very simple 2x2 models where Y11 = Y22 = -Y12 = -Y21, most real world elements cannot be modeled so simply. With transmission lines and real world inductor and capacitor models, for example, Y11 != -Y12, and for some more complex passive asymmetric elements Y11 != Y22. For many active linear devices, such as operational amplifiers, Y12 != Y21. Therefore, the example in this section uses independent Y11, Y12, Y21, and Y22 to illustrate the simulation processes that applies to more complex real world devices.

Each element Y parameter is inserted into the nodal admittance matrix by summing in them into the nodes they are attached to following the rules below.[9]

- Y11 is summed into the n x n node in the diagonal, where n is the node that the first pin, pin 1, is attached to.

If the second node is not 0, that is, not a ground:

- Y22 is summed into the m x m node in the diagonal, where m is the node that the second pin, pin 2, is attached to.

- Y12 is summed into the n x m node location

- Y21 is summed into the m x n node location

The table below shows the Chebyshev element 2x2 Y parameters summed in at the appropriate locations.

| node | 1 | 2 | 3 | 4 |

|---|---|---|---|---|

| 1 | L1_Y11 | L1_Y12 | ||

| 2 | L1_Y21 | L1_Y22+C1_Y11+L2_Y11 | L2_Y12 | |

| 3 | L2_Y21 | L2_Y22+C2_Y11+L3_Y11 | L3_Y12 | |

| 5 | L3_Y21 | L3_Y22 |

Nodal admittance matrix numerical entries

editTo simulate the filter at 1GHz, or any frequency, the element Y parameters must be converted to numerical entries using Y parameter models appropriate for the element installed. For ideal inductors and capacitors, the well known Y11 = Y22 = -Y12 = -Y21 = for inductors and Y11 = Y22 = -Y12 = -Y21 = for capacitors are sufficient. The numerical conversion are shown in the table below.

| node | 1 | 2 | 3 | 4 |

|---|---|---|---|---|

| 1 | -j0.0093682 | 0.0093682 | ||

| 2 | 0.0093682 | j0.00578933 | j0.00666462 | |

| 3 | j0.00666462 | j0.00578933 | 0.0093682 | |

| 4 | 0.0093682 | -j0.0093682 |

Removing internal nodes

editSince ports are only attached to node 1 and node 4, nodes 2 and 3 need to be removed through Kron reduction. The table below shows the reduced Y parameter matrix of the Chebyshev filter example simulation after nodes 2 and 4 are eliminated. The nodes of the reduced table are renumbered to 1 and 2.

| node | 1 | 2 |

|---|---|---|

| 1 | j0.0372422 | -j0.0536574 |

| 2 | -j0.0536574 | j0.0372422 |

Converting to an S parameter matrix

editSince the Chebyshev frequency response is observed from the S parameter matrix, namely |S12|, the next step is to convert the Y parameter matrix to an S parameter matrix, using well known Y matrix to S matrix conversions with the port impedance as the characteristic impedance (or characteristic admittance) for each node.

Simulated S parameters also allow for useful post simulation processing for things such as group delay and phase delay.

| node | 1 | 2 |

|---|---|---|

| 1 | -0.356328 + j0.280539 | 0.551322 + j0.700266 |

| 2 | 0.551322 + j0.700266 | -0.356328 + j0.280539 |

S parameter magnitudes

editSince the Chebyshev frequency response is expected to be observable in |S12| as a 1dB equi-ripple response from 0 to 1GHz, the complex S parameter entries need to be converted to their respective magnitudes, using the standard .

| node | 1 | 2 |

|---|---|---|

| 1 | 0.45351050 | 0.89125104 |

| 2 | 0.89125104 | 0.45351050 |

Check the results

editIt may be useful to do some quick validity checks at this point. Since the example Chebyshev filter design requirement is for -1dB attenuation at the cutoff frequency of 1GHz, |S12| at 1 GHz is expected to be -1dB. Furthermore, since all simulation elements are lossless, the well known relation, |S11|2+|S12|2 = 1[10] applies at all frequencies, including 1GHz.

| required condition | actual results | Status | |

|---|---|---|---|

| 1 | 20log10(|S12|) = -1dB | 20log10(0.89125104) = -1dB | Valid |

| 2 | |S12|2+|S12|2 = 1 | 0.453510502+0.891251042 = 1 | Valid |

Full frequency simulation

editThe final validity test for the example is to simulate the Chebyshev filter frequency response through the full useful range, which will be taken to be 100 MHz to 5 GHz for this case. This range should permit viewing of the equi-ripple |S12| of the pass band between 0 and -1 dB, somewhat steep stop band |S12| falling off at 1GHz, and an equi-ripple |S12| at the expected peak values of 20log10(.4535...) = -6.86825 dB.

Since all simulation outputs conform to the expected results, the Chebyshev filter example simulation is confirmed to be correct.

Simulating unterminated nodes

editSince S parameters require terminations on all nodes being simulated, simulating the S parameter value for unterminated nodes, such as the internal nodes of a network, are technically unsupported. However, placing a resistive termination on unterminated nodes that is large enough to not introduce any error of significance to make the nodes terminated is sufficient to accurately simulate the node. For example, the two internal nodes that were eliminated above could alternatively have had a 1e+09 ohm port attached to them, so instead of using Kron reduction to eliminate the nodes, the nodes could be accurately simulated with excessively large resistive ports.

Simulating zero resistance sources

editIf the input source to the network is an ideal voltage source with no resistance, the example above may be made to work by including a port resistance small enough to not introduce any error of significance. For example, a port with a resistance of 1e-09 in a network that is terminated elsewhere by 50 ohms would model an ideal source with sufficient accuracy.

Simulating the transfer function

editSince the example above simulates S parameters, another conversion is necessary to obtain the transfer function from S parameters. The conversion is, .[10]

See also

editConcepts:

HDL:

Lists:

- List of electrical engineering software

- List of free electronics circuit simulators

- Comparison of EDA software

Software:

References

edit- ^ "Disadvantages and Advantages of Simulations in Online Education". Archived from the original on 2010-12-16. Retrieved 2011-03-11.

- ^ Mengue and Vignat, Entry in the University of Marne, at Vallee

- ^ Fishwick, P. "Entry in the University of Florida". Archived from the original on 2000-05-19.

- ^ Pedro, J; Carvalho, N. "Entry in the Universidade de Aveiro, Portugal" (PDF). Archived from the original (PDF) on 2012-02-07. Retrieved 2007-04-27.

- ^ L. Walken and M. Bruckner, Event-Driven Multimodal Technology Archived 2007-05-05 at the Wayback Machine

- ^ Pejovic, P.; Maksimovic, D. (May 13, 1995). "A new algorithm for simulation of power electronic systems using piecewise-linear device models". IEEE Transactions on Power Electronics. 10 (3): 340–348. Bibcode:1995ITPE...10..340P. doi:10.1109/63.388000 – via IEEE Xplore.

- ^ Allmeling, J.H.; Hammer, W.P. (July 13, 1999). "PLECS-piece-wise linear electrical circuit simulation for Simulink". Proceedings of the IEEE 1999 International Conference on Power Electronics and Drive Systems. PEDS'99 (Cat. No.99TH8475). Vol. 1. pp. 355–360 vol.1. doi:10.1109/PEDS.1999.794588. ISBN 0-7803-5769-8. S2CID 111196369 – via IEEE Xplore.

- ^ Ohnari, Mikihiko (1998). Simulation engineering. Ohmsha. ISBN 9784274902178. Retrieved October 12, 2022.

- ^ Zelinger, G. (1966). Basic Matrix Analysis and Synthesis. Oxford, London, Edinburgh, New York, Toronto, Paris, Braunschweig: Pergamon Press, Ltd. pp. 45–58. ISBN 9781483199061.

- ^ a b Matthaei, George L.; Young, Leo; Jones, E. M. T. (1984). Microwave Filters, Impudence-Matching Networks, and Coupling Structures. 610 Washington Street, Dedham, Massachusetts, US: Artech House, Inc. (published 1985). p. 44. ISBN 0-89006-099-1.

{{cite book}}: CS1 maint: location (link)